- NXP Forums

- Product Forums

- General Purpose MicrocontrollersGeneral Purpose Microcontrollers

- i.MX Forumsi.MX Forums

- QorIQ Processing PlatformsQorIQ Processing Platforms

- Identification and SecurityIdentification and Security

- Power ManagementPower Management

- MCX Microcontrollers

- S32G

- S32K

- S32V

- MPC5xxx

- Other NXP Products

- Wireless Connectivity

- S12 / MagniV Microcontrollers

- Powertrain and Electrification Analog Drivers

- Sensors

- Vybrid Processors

- Digital Signal Controllers

- 8-bit Microcontrollers

- ColdFire/68K Microcontrollers and Processors

- PowerQUICC Processors

- OSBDM and TBDML

-

- Solution Forums

- Software Forums

- MCUXpresso Software and ToolsMCUXpresso Software and Tools

- CodeWarriorCodeWarrior

- MQX Software SolutionsMQX Software Solutions

- Model-Based Design Toolbox (MBDT)Model-Based Design Toolbox (MBDT)

- FreeMASTER

- eIQ Machine Learning Software

- Embedded Software and Tools Clinic

- S32 SDK

- S32 Design Studio

- Vigiles

- GUI Guider

- Zephyr Project

- Voice Technology

- Application Software Packs

- Secure Provisioning SDK (SPSDK)

- Processor Expert Software

-

- Topics

- Mobile Robotics - Drones and RoversMobile Robotics - Drones and Rovers

- NXP Training ContentNXP Training Content

- University ProgramsUniversity Programs

- Rapid IoT

- NXP Designs

- SafeAssure-Community

- OSS Security & Maintenance

- Using Our Community

-

- Cloud Lab Forums

-

- Home

- :

- Product Forums

- :

- S32G

- :

- Re: How to flash S32G399 M7 Core to boot from QSPI or any flash memory using Lauterbach

How to flash S32G399 M7 Core to boot from QSPI or any flash memory using Lauterbach

- Subscribe to RSS Feed

- Mark Topic as New

- Mark Topic as Read

- Float this Topic for Current User

- Bookmark

- Subscribe

- Mute

- Printer Friendly Page

How to flash S32G399 M7 Core to boot from QSPI or any flash memory using Lauterbach

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi, I have a S32G-VNP-RDB2 kit. I am trying to run a sample program for the M7 core to put data out of FlexCan0, which works when flashed to ram using Lauterbach with the script attached in the description. Now I am trying flash the elf file to non volatile memory but I am not successful in doing that yet. I changed the &load_to variable to flash as mentioned in the run.cmm script but haven't been successful for the M7 to boot from the flash. Any leads would be helpful thanks.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

When you are saying:

"I am trying flash the elf file to non volatile memory but I am not successful in doing that yet"

Are you flashing the whole blob image with the IVT structure? Or just the plain binary/elf? If so, S32G boot sequence might be different from other processors. It requires the creation of an IVT for it to boot from external memory. The creation of this structure is explained under the "Software Enablement Guide" available under the RDB2 product page (link: S32G2 Vehicle Networking Reference Design | NXP Semiconductors).

On regards of your debugger, we are not seeing any information for Lauterbach Flash programming at this moment, we do apologize. What we seem to find are the steps for S32 Debug Probe:

HOWTO: JTAG Flash Programming with S32 Debugger an... - NXP Community

There is also the possibility of flashing the external flash with the UART0 interface, could be useful.

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

The IVT will need the raw binary of your application, this is explained under the Software Enablement Guide. Still, let us know if you require more information on this regard.

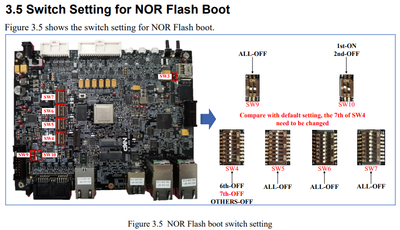

The configuration for QSPI boot under RDB2 is shared under the RDB2 User Guide:

This User Guide is available under the RDB2 product page (link: S32G2 Vehicle Networking Reference Design | NXP Semiconductors). But in summary, you are correct, all RCON values should be 0 and BOOTMOD value should be BOOTMOD[0] = 1 and BOOTMOD[1] = 0.

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi Daniel, I followed your advice and went through the documentation -Flashing Binaries to S32G-VNP-RDB3 Board and SOFTWARE ENABLEMENT GUIDE. I used the FreeRtos example for S32G3xx project which blinks led. I flashed this porject using Lauterbach to sram and led blinks as expected. Now my goal is to flash this in the nor flash so I create IVT bin file as mentioned enablement guide and flash the QSPI serially via uart0 successfully as attached in the screenshot. Also made sure the SW4 7th switch is off and SW10 1st switch ON and the 2nd off, also SW9 all off. Then I power cycle expecting to boot from qspi flash but I don't see the led blink which say's that it hasn't boot from the QSPI.

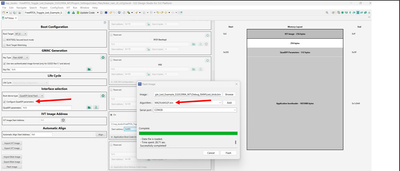

Attached Screenshots of the IVT configuration, the successful flash and the IVT mage blob

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

For the images you have provided, we found some problems with your IVT configuration.

The first problem is related to the QSPI parameters field. It seems you have enabled the QSPI parameters configuration but you are not sending any configuration in it. You can either send a configuration by selecting one from the following path:

"C:\nxp\S32DS.3.5\eclipse\mcu_data\processors\S32G399A\PlatformSDK_S32XX_2022_07\quadspi\default_boot_images"

This path can vary depending on the versions of the processor/IDE/RTD.

If you are following the SW Enablement Guide and modified the linker as per the guide, the QSPI parameters might not be required, since the size of the binary is smaller.

The second problem is related to the selection of the external NOR Flash, the one you are selecting is not embedded inside the RDB3, the one being used is the "MX25UM51245G/MX25UW51245G".

Also, we recommend looking into creating the IVT with a non-FreeRTOS example of blink ("Siul2_Dio_ToggleLed_S32G399A_M7"), for the simplicity.

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello So as per your suggestion I tried your suggestion I tried "Siul2_Dio_ToggleLed_S32G399A_M7"

and compiled it, unfortunately doesn't compile right, I removed the nano spec flag in the compile properties as well but still not successful.

Building file: ../generate/src/OsIf_Cfg.c

make: *** [src/subdir.mk:20: src/main.o] Error 1

make: *** Waiting for unfinished jobs....

arm-none-eabi-gcc.exe: fatal error: cannot read spec file 'nano.specs': No such file or directory

compilation terminated.

make: *** [generate/src/subdir.mk:25: generate/src/Clock_Ip_BOARD_InitPeripherals_PBcfg.o] Error 1

Invoking: Standard S32DS C Compiler

arm-none-eabi-gcc "@generate/src/Clock_Ip_BOARD_InitPeripherals_PBcfg.args" -MMD -MP -MF"generate/src/OsIf_Cfg.d" -MT"generate/src/OsIf_Cfg.o" -o "generate/src/OsIf_Cfg.o" "../generate/src/OsIf_Cfg.c"

arm-none-eabi-gcc.exe: fatal error: cannot read spec file 'nano.specs': No such file or directory

compilation terminated.

make: *** [generate/src/subdir.mk:26: generate/src/Clock_Ip_Cfg.o] Error 1

arm-none-eabi-gcc.exe: fatal error: cannot read spec file 'nano.specs': No such file or directory

compilation terminated.

make: *** [generate/src/subdir.mk:26: generate/src/OsIf_Cfg.o] Error 1

"make -j16 all" terminated with exit code 2. Build might be incomplete.

10:47:27 Build Failed. 5 errors, 0 warnings. (took 475ms)

Now going back to the FreeRtos example I followed your suggestion and changed the algorithm to MX25UM51245G and QSPI parameter is disabled.Still not successful to boot from the QSPI, I have attached the linker screenshot, Successful flash picture and the init vector table and the RCON and SW9 and SW10 switch configuration

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Seems odd, that your compilation is failing, since the example works out-of-the-box, once the code is generated from Config Tools.

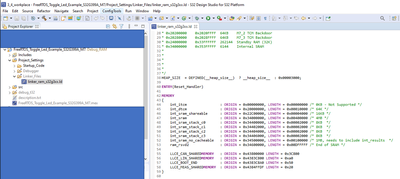

As for your IVT, it seems that you are modifying the linker of the example, since we can see that the default linker is as follows:

Also, the linker does not seem to follow the SW Enablement Guide. Can you confirm that following the linker used under the SW enablement guide provides the same result?

There is a default MPU configuration being loaded to each example, if the MPU is not modified. You could also try and disable the MPU to understand if this is related to it.

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Thanks for your feedback. We seem to see that you are using the default linker of the example, not the SW Enablement Guide modified linker. If you are using the default linker, you are required to load a QSPI reconfiguration parameters binary, since the image is too big and the deafult QSPI speed is not enough to comply with the following S32G requirement [Page 1347, S32G2 Reference Manual, Rev. 7, February 2023]:

"BootROM sets a timeout of 500ms when downloading the application image. User must ensure that the maximum image size can be downloaded within this time. The image size would depend on the configuration used."

If you are looking for the QSPI reconfiguration parameters binary, you should see them available under the following path:

"C:\nxp\S32DS.3.4\eclipse\mcu_data\processors\S32G274A_Rev2\PlatformSDK_S32XX_2022_03\quadspi\default_boot_images"

Where it can vary depending on which IDE/RTD version you have installed.

Also, the example does not configure clocks. When you load it from QSPI, you will see that the LED toggles slower than when using a debugger. This, as said before, is due to the clocks not being configured.

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thanks a ton Daniel ! It worked as you mentioned the led toggles really slow. Is there an example of how to configure the clock for QSPI ? If I use emmc would I still need to configure clock ?

Also it would be really helpful to know the actual reason why the led toggles slow, like I assume the bootrom loads the code from QSPI to sram to execute how does the clock come into picture here ?

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

We may not have explained correctly the situation. This is due to selecting an external interface to boot, not using the debugger. As for how to initialize the clocks, the SW enablement guide provides under Page 16 some steps to add the clock initialization to the code. You can also reuse the clock initialization from a different example (like UART).

The explanation is that the BootROM requires to configure the clocks in a certain way so that it can complete its objective. If no reconfiguration is done, then the clocks will remain how the BootROM configured them.

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hi,

Which example of UART did you use?

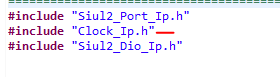

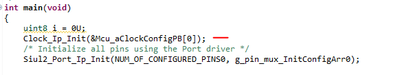

We copy the following code and see the LED blinking at the expected speed:

This was copied from the "Linflexd_Uart_Ip_Example_S32G274A_M7", since it is the non-AUTOSAR example.

Please, let us know.

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Hello I got Siul2_Dio_ToggleLed_S32G399A_M7 default project (no changes ) compiling and used Lauterbach and checked the RGB led blinks so that is good. Now I follow the steps mentioned in the application node to create the blob and flash QSPI via the uart. Turn the power off, have all RCON bits low and the SW10 1st switch ON and the 2nd off, also SW9 all off. Turned it back on the RGB led doesn't toggle. Attached are the binary executable and blobs

I have attached 4 attachment here. Siul2_Dio_ToggleLed_S32G399A_M7.bin is the bin file generated on building. Siul2_Dio_ToggleLed_S32G399A_M7_bl.bin is the exported bin file from Step 9 of LIGHT UP RGB LED: MAKE IMAGE BY IVT TOOL. Siul2_Dio_ToggleLed_S32G399A_M7_blob.bin is the final blob bin. Also attached the setup picture here

I am creating a separate reply for other attachment as I can only attach 5 in this reply

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

- Mark as New

- Bookmark

- Subscribe

- Mute

- Subscribe to RSS Feed

- Permalink

- Report Inappropriate Content

Thank you let me give it a try