**ON Semiconductor**

Is Now

# Onsemi

To learn more about onsemi<sup>™</sup>, please visit our website at <u>www.onsemi.com</u>

onsemi and ONSEMI. and other names, marks, and brands are registered and/or common law trademarks of Semiconductor Components Industries, LLC dba "onsemi" or its affiliates and/or subsidiaries in the United States and/or other countries. onsemi owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of onsemi product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. onsemi reserves the right to make changes at any time to any products or information herein, without notice. The information herein is provided "as-is" and onsemi makes no warranty, representation or guarantee regarding the accuracy of the information, product factures, availability, functionality, or suitability of its products for any particular purpose, nor does onsemi assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using onsemi products, including compliance with all laws, regulations and asfety requirements or standards, regardless of any support or applications information provided by onsemi. "Typical" parameters which may be provided in onsemi data sheets and/or by customer's technical experts. onsemi products and actal performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. onsemi products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use onsemi products for any such unintended or unauthorized application, Buyer shall indemnify and hold onsemi and its officers, employees, subsidiari

# NCS36510 Programming Manual

# **DEVICE OVERVIEW**

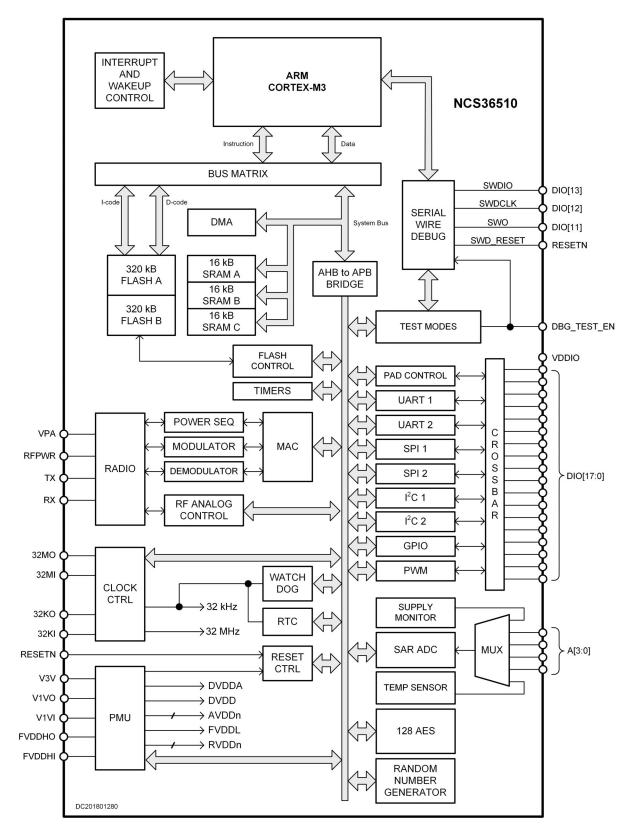

NCS36510 is an ultra-low power RF microcontroller System on Chip (SoC) that integrates the powerful and energy efficient ARM<sup>®</sup> Cortex<sup>®</sup>-M3 microprocessor, 640 kB of FLASH memory, 48 kB of RAM, 2.4 GHz 802.15.4 RF transceiver with hardware accelerated MAC, a DMA controller, and 18 GPIO. Peripherals include: UART (2), SPI (2), I<sup>2</sup>C (2), timers (3), PWM, RTC, 10-bit SAR ADC, and internal voltage and temperature sensors. Security features include 128/256 hardware accelerated AES encryption engine and a true random number generator. NCS36510 implements advanced low-power modes for ultra-low power consumption.

# Features

ARM® Cortex® –M3

- ARMv7–M Architecture

- Thumb® / Thumb-2 Subset Instruction Set

- Nested Vectored Interrupt Controller (NVIC) with 15 Built–in Exceptions and 20 External Interrupts with 4–bit Programmable Priority

- Non-Maskable Interrupt (NMI)

- Sleep, Deep Sleep, and Coma Mode Support

- Wake-up Interrupt Controller (WIC)

- SysTick Timer for Scheduler

- Bit Banding

- Little Endian

# Debugger

- Serial-Wire Debug Access Port (SW-DAP)

- Breakpoint and Single Stepping Support

- Micro Trace Buffer (MTB)

- Standard Trace with ITM and DWT Triggers and Counters

- Full Debug with DWT Matching

- Debug Part Lockout

# Memory

- 640 kB FLASH

- Single Cycle 32-bit Fetch @ 32 MHz

- Two Banks of 320 kB with Independent Power Controls

- Both Banks Have Their Own 8 kB Onformation Block Section

- ♦ 10,000 Program/Erase Cycles

- 10 Year Data Retention at 85C

# **ON Semiconductor®**

www.onsemi.com

# **APPLICATION NOTE**

- 48 kB RAM

- 16 kB or 32 kB Can be Retained in Coma Mode Flexible Clocking

- On-Chip High Speed (32 MHz) RC Oscillator

- On-Chip Low Power (32.768 kHz) RC Oscillator

- High Speed Crystal Oscillator (32 MHz)

- Low Power Crystal Oscillator (32.768 kHz)

- Automatic Calibration of On-Chip RC Oscillators to External High Speed Crystal Oscillator Timers

- General Purpose 16-bit Timers (3)

- ♦ Pre-Load

- Down Count

- Interrupt on 0

- Pre-scale Clock Divider

- Free Running or Periodic Mode

- Integrated SysTick Timer

- Real Time Clock

- On 32.768 kHz Clock Domain

- Pre–Load

- 15 bit Sub–Seconds Counter

- 32 bit Seconds Counter

- Both Counters Can Be Combined for ~ 136 Years and Can Implement a UNIX (POSIX or Epoch) Time Counter

- Watchdog Timer

- On 32.768 kHz Clock Domain

- ♦ Pre-Load

- Max Timeout 30.5 us

- Lockout Control

# 18 GPIO

- Programmable pull-up/pull-down

- Programmable drive strengths

- Open drain capable

- Programmable interrupts (edge/level, polarity)

- Allocation of GPIOn pins to peripherals through programmable crossbar

# UART (2x)

- One full featured 16550 UART

- One reduced feature UART with transmit, receive, clear to send, and ready to send

- Programmable baud rate

# Master/Slave SPI

- Programmable data width and direction

- Programmable phase and polarity

# 10-bit SAR ADC

- 10-bit 200 k-samples/second @ 4 Mhz

- Up to 4 external sample channels

- Single ended sampling

- Pseudo-differential sampling mode

- Ratio sampling mode

- Programmable input resistor divider

- Can sample internal power supply voltage and built-in temperature sensor

# **Security Features**

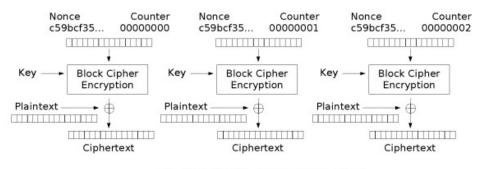

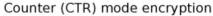

- Hardware AES Acceleration

- Supports 128-bit and 256-bit encryption/decryption

- CCM, CTR, and CBC modes

- True random number generator

- Debug port lock

| Table of Contents                                                 |    |

|-------------------------------------------------------------------|----|

| Block Diagram                                                     | 4  |

| Cortex-M3 Instruction Set Summary                                 | 5  |

| Cortex-M3 Microcontroller and Bus Fabric                          | 9  |

| Метогу Мар                                                        |    |

| DBG_Test_EN PIN                                                   |    |

| Flash Controller                                                  |    |

| Reset and Brownout Control                                        |    |

| Clocks                                                            |    |

| Timers                                                            |    |

| Digital Input / Output (Dio) Control                              |    |

| Crossbar Control                                                  |    |

| Direct Memory Access (DMA) Controller                             |    |

| 10 bit Successive Approximation (SAR) Analog to Digital Converter | 45 |

| PWM                                                               |    |

| IEEE 802.15.4 MAC                                                 | 49 |

| Radio Frequency (RF) Control                                      | 68 |

| Test Mode Control                                                 | 70 |

| Power Management                                                  |    |

| External Communication Interfaces                                 |    |

| Security Functions                                                | 83 |

|                                                                   |    |

# **BLOCK DIAGRAM**

Figure 1. Block Diagram

# **CORTEX-M3 INSTRUCTION SET SUMMARY**

The processor implements the ARMv7-M Thumb instruction set, including a number of 32-bit instructions that use Thumb-2 technology. The Cortex-M3 instruction set comprises:

- All of the 16-bit Thumb instructions from ARMv6 excluding SETEND and BLX.

- The 32-bit Thumb instructions excluding instructions related to Co-processor support (not supported on Cortex-M3) and the following HINT instructions (which behave as NOP if used): DBG, PLD, PLI, and YIELD.

The following instruction set summary is provided by ARM online at: https://developer.arm.com/docs/ddi0337/latest/programme rs-model/instruction-set-summary/cortex-m3-instruction s and is provided here for convenience.

The following table shows the Cortex-M3 instructions and their cycle counts. The cycle counts are based on a system with zero wait states.

Within the assembler syntax, depending on the operation, the <op2> field can be replaced with one of the following options:

• a simple register specifier, for example Rm

Table 1. Cortex-M3 Instruction Set Table

- an immediate shifted register, for example Rm, LSL #4

- a register shifted register, for example Rm, LSL R<sub>S</sub>

- an immediate value, for example #0xE000E000. For brevity, not all load and store addressing modes are shown.

The table below uses the following abbreviations in the Cycles column:

- P: The number of cycles required for a pipeline refill. This ranges from 1 to 3 depending on the alignment and width of the target instruction, and whether the processor manages to speculate the address early.

- B: The number of cycles required to perform the barrier operation. For and DSB and DMB, the minimum number of cycles is zero. For ISB, the minimum number of cycles is equivalent to the number required for a pipeline refill.

- N: The number of registers in the register list to be loaded or stored, including PC or LR.

- W: The number of cycles spent waiting for an appropriate event.

See the ARMv7-M Architecture Reference Manual for more information about the ARMv7-M Thumb instructions.

| Operation     | Description              | Assembler                           | Cycles           |

|---------------|--------------------------|-------------------------------------|------------------|

|               | Register                 | MOV Rd, <op2></op2>                 | 1                |

| Maura         | 16-bit immediate         | MOVW Rd, # <imm></imm>              | 1                |

| Move          | Immediate into top       | MOVT Rd, # <imm></imm>              | 1                |

|               | To PC                    | MOV PC, Rm                          | 1 + P            |

|               | Add                      | ADD Rd, Rn, <op2></op2>             | 1                |

| <b>A</b> .1.1 | Add to PC                | ADD PC, PC, Rm                      | 1 + P            |

| Add           | Add with carry           | ADC Rd, Rn, <op2></op2>             | 1                |

|               | Form address             | ADR Rd, <label></label>             | 1                |

|               | Subtract                 | SUB Rd, Rn, <op2></op2>             | 1                |

| Subtract      | Subtract with borrow     | SBC Rd, Rn, <op2></op2>             | 1                |

|               | Reverse                  | RSB Rd, Rn, <op2></op2>             | 1                |

|               | Multiply                 | MUL Rd, Rn, Rm                      | 1                |

|               | Multiply accumulate      | MLA Rd, Rn, Rm                      | 2                |

|               | Multiply subtract        | MLS Rd, Rn, Rm                      | 2                |

| Multiply      | Long signed              | SMULL RdLo, RdHi, Rn, Rm            | 3 to 5 (Note 1)  |

|               | Long unsigned            | UMULL RdLo, RdHi, Rn, Rm            | 3 to 5 (Note 1)  |

|               | Long signed accumulate   | SMLAL RdLo, RdHi, Rn, Rm            | 4 to 7 (Note 1)  |

|               | Long unsigned accumulate | UMLAL RdLo, RdHi, Rn, Rm            | 4 to 7 (Note 1)  |

|               | Signed                   | SDIV Rd, Rn, Rm                     | 2 to 12 (Note 2) |

| Divide        | Unsigned                 | UDIV Rd, Rn, Rm                     | 2 to 12 (Note 2) |

| Osturata      | Signed                   | SSAT Rd, # <imm>, <op2></op2></imm> | 1                |

| Saturate      | Unsigned                 | USAT Rd, # <imm>, <op2></op2></imm> | 1                |

# Table 1. Cortex-M3 Instruction Set Table

| Operation | Description                 | Assembler                          | Cycles         |

|-----------|-----------------------------|------------------------------------|----------------|

| Compare   | Compare CMP Rn, <op2></op2> |                                    | 1              |

| Compare   | Negative                    | CMN Rn, <op2></op2>                | 1              |

|           | AND                         | AND Rd, Rn, <op2></op2>            | 1              |

|           | Exclusive OR                | EOR Rd, Rn, <op2></op2>            | 1              |

|           | OR                          | ORR Rd, Rn, <op2></op2>            | 1              |

| Lesier    | OR NOT                      | ORN Rd, Rn, <op2></op2>            | 1              |

| Logical   | Bit clear                   | BIC Rd, Rn, <op2></op2>            | 1              |

|           | Move NOT                    | MVN Rd, <op2></op2>                | 1              |

|           | AND test                    | TST Rn, <op2></op2>                | 1              |

|           | Exclusive OR test           | TEQ Rn, <op1></op1>                |                |

|           | Logical shift left          | LSL Rd, Rn, # <imm></imm>          | 1              |

|           | Logical shift left          | LSL Rd, Rn, Rs                     | 1              |

|           | Logical shift right         | LSR Rd, Rn, # <imm></imm>          | 1              |

| Shift     | Logical shift right         | LSR Rd, Rn, Rs                     | 1              |

|           | Arithmetic shift right      | ASR Rd, Rn, # <imm></imm>          | 1              |

|           | Arithmetic shift right      | ASR Rd, Rn, Rs                     | 1              |

|           | Rotate right                | ROR Rd, Rn, # <imm></imm>          | 1              |

| Rotate    | Rotate right                | ROR Rd, Rn, Rs                     | 1              |

|           | With extension              | RRX Rd, Rn                         | 1              |

| Count     | Leading zeroes              | CLZ Rd, Rn                         | 1              |

|           | Word                        | LDR Rd, [Rn, <op2>]</op2>          | 2 (Note 3)     |

|           | To PC                       | LDR PC, [Rn, <op2>]</op2>          | 2 (Note 3) + P |

|           | Halfword                    | LDRH Rd, [Rn, <op2>]</op2>         | 2 (Note 3)     |

|           | Byte                        | LDRB Rd, [Rn, <op2>]</op2>         | 2 (Note 3)     |

|           | Signed halfword             | LDRSH Rd, [Rn, <op2>]</op2>        | 2 (Note 3)     |

|           | Signed byte                 | LDRSB Rd, [Rn, <op2>]</op2>        | 2 (Note 3)     |

|           | User word                   | LDRT Rd, [Rn, # <imm>]</imm>       | 2 (Note 3)     |

| Load      | User halfword               | LDRHT Rd, [Rn, # <imm>]</imm>      | 2 (Note 3)     |

|           | User byte                   | LDRBT Rd, [Rn, # <imm>]</imm>      | 2 (Note 3)     |

|           | User signed halfword        | LDRSHT Rd, [Rn, # <imm>]</imm>     | 2 (Note 3)     |

|           | User signed byte            | LDRSBT Rd, [Rn, # <imm>]</imm>     | 2 (Note 3)     |

|           | PC relative                 | LDR Rd,[PC, # <imm>]</imm>         | 2 (Note 3)     |

|           | Doubleword                  | LDRD Rd, Rd, [Rn, # <imm>]</imm>   | 1 + N          |

|           | Multiple                    | LDM Rn, { <reglist>}</reglist>     | 1 + N          |

|           | Multiple including PC       | LDM Rn, { <reglist>, PC}</reglist> | 1 + N + P      |

|           | Word                        | STR Rd, [Rn, <op2>]</op2>          | 2 (Note 3)     |

|           | Halfword                    | STRH Rd, [Rn, <op2>]</op2>         | 2 (Note 3)     |

|           | Byte                        | STRB Rd, [Rn, <op2>]</op2>         | 2 (Note 3)     |

|           | Signed halfword             | STRSH Rd, [Rn, <op2>]</op2>        | 2 (Note 3)     |

|           | Signed byte                 | STRSB Rd, [Rn, <op2>]</op2>        | 2 (Note 3)     |

|           | User word                   | STRT Rd, [Rn, # <imm>]</imm>       | 2 (Note 3)     |

|           |                             |                                    |                |

# Table 1. Cortex-M3 Instruction Set Table

| Operation    | Description             | Assembler                                    | Cycles              |

|--------------|-------------------------|----------------------------------------------|---------------------|

|              | User byte               | STRBT Rd, [Rn, # <imm>]</imm>                | 2 (Note 3)          |

|              | User signed halfword    | STRSHT Rd, [Rn, # <imm>]</imm>               | 2 (Note 3)          |

|              | User signed byte        | STRSBT Rd, [Rn, # <imm>]</imm>               | 2 (Note 3)          |

|              | Doubleword              | STRD Rd, Rd, [Rn, # <imm>]</imm>             | 1 + N               |

|              | Multiple                | STM Rn, { <reglist>}</reglist>               | 1 + N               |

|              | Push                    | PUSH { <reglist>}</reglist>                  | 1 + N               |

| Push         | Push with link register | PUSH { <reglist>, LR}</reglist>              | 1 + N               |

| _            | Рор                     | POP { <reglist>}</reglist>                   | 1 + N               |

| Рор          | Pop and return          | POP { <reglist>, PC}</reglist>               | 1 + N + P           |

|              | Load exclusive          | LDREX Rd, [Rn, # <imm>]</imm>                | 2                   |

|              | Load exclusive half     | LDREXH Rd, [Rn]                              | 2                   |

|              | Load exclusive byte     | LDREXB Rd, [Rn]                              | 2                   |

| Semaphore    | Store exclusive         | STREX Rd, Rt, [Rn, # <imm>]</imm>            | 2                   |

|              | Store exclusive half    | STREXH Rd, Rt, [Rn]                          | 2                   |

|              | Store exclusive byte    | STREXB Rd, Rt, [Rn]                          | 2                   |

|              | Clear exclusive monitor | CLREX                                        | 1                   |

|              | Conditional             | B <cc> <label></label></cc>                  | 1 or 1 + P (Note 4) |

|              | Unconditional           | B <label></label>                            | 1 + P               |

|              | With link               | BL <label></label>                           | 1 + P               |

|              | With exchange           | BX Rm                                        | 1 + P               |

| Branch       | With link and exchange  | BLX Rm                                       | 1 + P               |

|              | Branch if zero          | CBZ Rn, <label></label>                      | 1 or 1 + P (Note 4) |

|              | Branch if non-zero      | CBNZ Rn, <label></label>                     | 1 or 1 + P (Note 4) |

|              | Byte table branch       | TBB [Rn, Rm]                                 | 2 + P               |

|              | Halfword table branch   | TBH [Rn, Rm, LSL#1]                          | 2 + P               |

|              | Supervisor call         | SVC # <imm></imm>                            | _                   |

|              | If-then-else            | IT <cond></cond>                             | 1 (Note 5)          |

|              | Disable interrupts      | CPSID <flags></flags>                        | 1 or 2              |

| State change | Enable interrupts       | CPSIE <flags></flags>                        | 1 or 2              |

|              | Read special register   | MRS Rd, <specreg></specreg>                  | 1 or 2              |

|              | Write special register  | MSR <specreg>, Rn</specreg>                  | 1 or 2              |

|              | Breakpoint              | BKPT # <imm></imm>                           | -                   |

|              | Signed halfword to word | SXTH Rd, <op2></op2>                         | 1                   |

|              | Signed byte to word     | SXTB Rd, <op2></op2>                         | 1                   |

| Extend       | Unsigned halfword       | UXTH Rd, <op2></op2>                         | 1                   |

|              | Unsigned byte           | UXTB Rd, <op2></op2>                         | 1                   |

|              | Extract unsigned        | UBFX Rd, Rn, # <imm>,<br/>#<imm></imm></imm> | 1                   |

| Bit field    | Extract signed          | SBFX Rd, Rn, # <imm>,<br/>#<imm></imm></imm> | 1                   |

|              | Clear                   | BFC Rd, Rn, # <imm>,<br/>#<imm></imm></imm>  | 1                   |

|              | Insert                  | BFI Rd, Rn, # <imm>, #<imm></imm></imm>      | 1                   |

### Table 1. Cortex–M3 Instruction Set Table

| Operation | Description                 | Assembler           | Cycles |

|-----------|-----------------------------|---------------------|--------|

|           | Bytes in word               | REV Rd, Rm          | 1      |

| Deverse   | Bytes in both halfwords     | REV16 Rd, Rm        | 1      |

| Reverse   | Signed bottom halfword      | REVSH Rd, Rm        | 1      |

|           | Bits in word                | RBIT Rd, Rm         | 1      |

|           | Send event                  | SEV                 | 1      |

|           | Wait for event              | WFE                 | 1 + W  |

| Hint      | Wait for interrupt          | WFI                 | 1 + W  |

|           | No operation                | NOP                 | 1      |

|           | Instruction synchronization | ISB                 | 1 + B  |

| Barriers  | Data memory                 | DMB                 | 1 + B  |

|           | Data synchronization        | DSB <flags></flags> | 1 + B  |

1. UMULL, SMULL, UMLAL, and SMLAL instructions use early termination depending on the size of the source values. These are interruptible, that is abandoned and restarted, with worst case latency of one cycle.

2. Division operations use early termination to minimize the number of cycles required based on the number of leading ones and zeroes in the input operands.

3. Neighboring load and store single instructions can pipeline their address and data phases. This enables these instructions to complete in a single execution cycle.

4. Conditional branch completes in a single cycle if the branch is not taken.

5. An IT instruction can be folded onto a preceding 16-bit Thumb instruction, enabling execution in zero cycles.

# CORTEX-M3 MICROCONTROLLER AND BUS FABRIC

NCS36510 integrates the powerful and energy efficient ARM Cortex–M3 processor that includes the integrated Nested Vectored Interrupt Controller (NVIC), Wake–up Interrupt Controller (WIC), and Debug Access Port (DAP). The processor uses the Thumb instruction set and is optimized for high performance with reduced code size and low power operation. The ARM Cortex–M3 efficiently handles multiple parallel peripherals and has integrated sleep modes. With industry standard tool chain and support, developing applications on the NCS36510 platform reduces time to market. Test and debug capability is enhanced with the ARM Serial Wire Debug Port with full debug capabilities. The microprocessor uses little–endian formatting.

The NCS36510 implementation of the ARM Cortex–M3 includes a 640 kB integrated FLASH memory (2 banks of 320 kB) with 48 kB of internal RAM memory (3 banks of 16 kB, 1 or 2 retainable in coma mode). The microprocessor, debug port, and memories are interconnected using the Advanced Microcontroller Bus Architecture (AMBA bus) AHB–Lite system interface bus. An AHB to APB Bridge is included to connect the peripherals.

Next to the regular ARM Cortex–M3 processor interrupts, the NCS36510 implements multiple external source interrupts for peripheral devices. A powerful nested, pre–emptive and priority based interrupt handling assure timely and flexible response to external events.

Low power features on NCS36510 include the WIC, adjustable clock rates, and different software controlled power modes to maximize opportunities to save power in final application.

### Serial Wire Debug Access Port (SW-DAP)

The Debug Access Port (DAP) is included in this ARM Cortex–M3 implementation. Standard ARM Cortex–M3 Serial Wire Debugging (SWD) debugging is supported by NCS36510. JTAG is not supported

The NCS36510 implements full trace support for the Cortex–M3 which includes the Data Watchpoint and Trace Unit (DWT) with comparators and counters, Instrumentation Trace Macrocell (ITM), and Embedded Trace Macrocell (ETM).

The Trace Port Interface Unit (TPIU) supports Serial Wire Viewer (SWV) mode.

Refer to the ARM Cortex–M3 technical reference manual for a full definition of the debug system and its capabilities.

The Debug Port is disabled at power-up if the part is locked, and may be enabled by firmware. Driving the DBG\_TEST\_EN pin high will prevent the part from entering coma mode (see the PMU description).

The Debug Access Port interface implementation is the ARM Serial Wire Debug Port (SW–DP) connected to pins DIO[13] (SWCLK), DIO[12] (SWDIO), and DIO[11] (SWO). To enable the DAP drive the DBG\_TEST\_EN pin high and DIO[13] and DIO[12] are automatically reconfigured for DAP usage. The DIO[11] pin will only connect to SWO if the TRCENA bit is enabled.

Use any SWD compliant hardware debugger interface to interact with the internals of the NCS36510.

NCS36510 is optimized for battery powered applications and therefore uses reduced size digital drivers in the DIO pins. In 3V mode, the maximum practical DAP speed is 1 MHz. Adding external buffers could increase this speed but on the ON Semiconductor development board an upper reliable limit has been found at 1MHz.

Not all, if any, SWD debuggers support 1V mode operation.

### **Nested Vectored Interrupt Controller (NVIC)**

The Cortex–M3 Nested Vectored Interrupt Controller (NVIC) supports priority based nested vectored interrupts. It includes 15 built–in or reserved exceptions and is configured with an additional 20 interrupts. Most interrupts have programmable priority. Priority levels available in the NVIC are 0, 64, 128, and 192. Lower numbers are higher priority. The priority of each group can be set separately by the firmware. While an interrupt is being serviced, only interrupts from a higher priority arrive at the same time, the earlier one (according to polling order) will be serviced first. The optional Wake–up Interrupt Controller (WIC) is included for low power mode support. Only a subset of the interrupts are included in the wake–up controller.

| Exception Number | Exception Type    | Priority     | Description                                                                     |

|------------------|-------------------|--------------|---------------------------------------------------------------------------------|

| 1                | Reset             | -3 (Highest) | Reset                                                                           |

| 2                | NMI               | -2           | Non-maskable interrupt. This<br>is set to the watchdog inter-<br>rupt.          |

| 3                | Hard fault        | -1           | All fault conditions if the corre-<br>sponding fault handler is not<br>enabled. |

| 4                | MemManage fault   | Programmable | Memory management fault                                                         |

| 5                | Bus fault         | Programmable | Bus fault                                                                       |

| 6                | Usage fault       | Programmable | Exceptions resulting from pro-<br>gram error.                                   |

| 7–10             | Reserved          |              |                                                                                 |

| 11               | SVC               | Programmable | Supervisor Call                                                                 |

| 12               | Debug Monitor     | Programmable | Debug monitor (breakpoints,<br>watchpoints, or external debug<br>requests)      |

| 13               | Reserved          | Programmable |                                                                                 |

| 14               | PendSV            | Programmable | Pendable Service Call                                                           |

| 15               | SYSTICK           | Programmable | System Tick Timer                                                               |

| 16               | Timer 0           | Programmable | Timer 0 interrupt                                                               |

| 17               | Timer 1           | Programmable | Timer 1 interrupt                                                               |

| 18               | Timer 2           | Programmable | Timer 2 interrupt                                                               |

| 19               | UART              | Programmable | UART interrupt                                                                  |

| 20               | SPI               | Programmable | SPI interrupt                                                                   |

| 21               | I2C               | Programmable | I2C interrupt                                                                   |

| 22               | GPIO              | Programmable | GPIO interrupt                                                                  |

| 23               | RTC               | Programmable | Real-time-clock interrupt                                                       |

| 24               | Flash Controller  | Programmable | Flash Controller.                                                               |

| 25               | MAC               | Programmable | MAC interrupt                                                                   |

| 26               | AES               | Programmable | AES interrupt                                                                   |

| 27               | ADC               | Programmable | ADC interrupt                                                                   |

| 28               | Clock Calibration | Programmable | Clock calibration interrupt                                                     |

| 29               | UART #2           | Programmable | UART Interrupt                                                                  |

| 30               | UVI               | Programmable | Under Voltage Indicator Inter-<br>rupt                                          |

| 31               | DMA               | Programmable | DMA interrupt                                                                   |

| 32               | CDBGPWRUPREQ      | Programmable | Debug request                                                                   |

| 33               | SPI #2            | Programmable | SPI #2 Interrupt                                                                |

| 34               | I2C #2            | Programmable | I2C #2 Interrupt                                                                |

| 35               | FVDDH Comp        | Programmable | FVDDH Supply Comparator<br>Trip                                                 |

### Table 2. Cortex–M3 Instruction Set Table

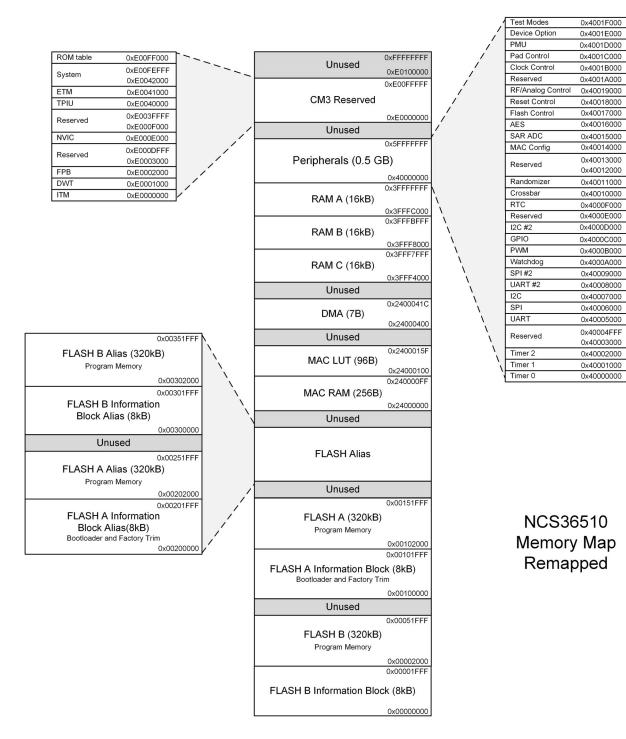

# **MEMORY MAP**

The 32 bit memory address space is broken up into regions for code, data, and multi-use. Memory elements consist of registers, RAM, and FLASH. A memory region is dedicated to the IOP and APB peripheral access. There are also regions for built in Cortex-M3 registers and NCS36510 peripherals. As in most Cortex-M3 designs there are many unused portions of the memory space. Individual memory regions and elements are described in subsequent sections.

# Flash

NCS36510 contains a total of 640 kB of FLASH memory, organized as two banks of 320 kB each (81,920 words by 32 bits). Two independent FLASH banks are used to allow either OTA upgrades or dual stack applications. If a FLASH bank is unused, it can be powered down to save power.

Both main FLASH banks include an additional 8 kB information block (2048 words by 32 bits).

By default the FLASH A information block contains the bootloader and factory programmed trim values. There are a minimum of three application related trims that can be programmed by the customer: 32.768 kHz external oscillator, 32 MHz external oscillator, and the RSSI offset. These application trims can be determined during the design phase, and for a given PCB design they can be set to a constant value for all boards of the same design. At the factory these are set to a nominal value.

The bootloader is also stored in the FLASH A information block. To reprogram the bootloader it is required to drive the DBG\_TEST\_EN pin high and to write an unlock code to the FLASH. The factory trim contents must be read out, the entire FLASH information block erased, and then the bootloader and factory trims written back in. If the factory trims are lost on a device it will become inoperable as factory trims are not recoverable.

The FLASH B information block does not contain any factory trim information.

# Flash Alias and Remap

NCS36510 has a FLASH remap feature that allows the FLASH A and FLASH B to change positions in the memory map when activated. This makes it easier to reboot the system from FLASH B if doing over the air firmware updates.

Another related feature is the FLASH alias. The FLASH alias allows the FLASH A and FLASH B contents to be visible in a fixed address space regardless of the remap setting.

Both FLASH remap and alias features are shown in the memory map diagrams.

During ON Semiconductor factory test, the factory trim values and bootloader are written to the FLASH A information block. No factory information is written to the FLASH B information block. Software must be careful when using the FLASH remap feature as the factory trims and bootloader could be missed since FLASH A and FLASH B change places in the memory map. An easy way to avoid issues is to use the FLASH A information block alias during boot up because the alias memory map does not depend on the remap setting. The ON Semiconductor software already takes care of this remap functionality, but this feature is important to understand for customers writing their own software.

# RAM

The NCS36510 has three banks of 16kB each RAM. In coma mode either one or two of these banks can be retained.

Test Modes

0x4001F000 0x4001E000

|                             |            |                                                              |                                                         | ,   | Test Modes        | 0X4001F000               |

|-----------------------------|------------|--------------------------------------------------------------|---------------------------------------------------------|-----|-------------------|--------------------------|

|                             |            |                                                              |                                                         | /   | Device Option     | 0x4001E000               |

|                             |            |                                                              |                                                         | i   | PMU               | 0x4001D000               |

| ROM table 0xE00FF0          | 00         |                                                              | 0xFFFFFFFF                                              |     | Pad Control       | 0x4001C000               |

|                             |            | Unused                                                       | 0xE0100000                                              |     | Clock Control     | 0x4001B000               |

| System 0xE00420             |            |                                                              |                                                         |     | Reserved          | 0x4001A000               |

| ETM 0xE00410                |            |                                                              | 0xE00FFFFF                                              | · / | RF/Analog Control | 0x40019000               |

| TPIU 0xE00400               |            | CM3 Reserved                                                 |                                                         | i   | Reset Control     | 0x40018000               |

|                             |            | 486003-8976 (65476-05-07) (966008)                           |                                                         | 1   | Flash Control     | 0x40017000               |

| Reserved 0xE003FF           |            |                                                              | 0xE0000000                                              | 1   | AES               | 0x40016000               |

| 0xE000F0                    |            | Unused                                                       |                                                         | /   | SAR ADC           |                          |

| NVIC 0xE000E0               | _ /        |                                                              | 0x5FFFFFFF                                              | ſ   |                   | 0x40015000<br>0x40014000 |

| Reserved 0xE000DF           |            |                                                              |                                                         |     | MAC Config        |                          |

| 0xE00030                    |            | Peripherals (0.5 G                                           | iB)                                                     |     | Reserved          | 0x40013000               |

| FPB 0xE00020                | 00         |                                                              | 0x40000000                                              |     |                   | 0x40012000               |

| DWT 0xE00010                | 00         |                                                              | 0x3FFFFFFF                                              | l   | Randomizer        | 0x40011000               |

| ITM 0xE00000                | 00         | RAM A (16kB)                                                 | 0,0111111                                               | È.  | Crossbar          | 0x40010000               |

|                             |            |                                                              | 0                                                       | l`\ | RTC               | 0x4000F000               |

|                             |            |                                                              | 0x3FFFC000<br>0x3FFFBFFF                                |     | Reserved          | 0x4000E000               |

|                             |            |                                                              | UX3FFFBFFF                                              |     | I2C #2            | 0x4000D000               |

|                             |            | RAM B (16kB)                                                 |                                                         | i i | GPIO              | 0x4000C000               |

|                             |            |                                                              | 0x3FFF8000<br>0x3FFF7FFF                                | ι N | PWM               | 0x4000B000               |

|                             |            | DAM C (16kB)                                                 | UX3FFF/FFF                                              | ١   | Watchdog          | 0x4000A000               |

|                             |            | RAM C (16kB)                                                 |                                                         | ١   | SPI#2             | 0x40009000               |

|                             |            |                                                              | 0x3FFF4000                                              | . \ | UART #2           | 0x40008000               |

|                             |            | Unused                                                       |                                                         | N 1 | 12C               | 0x40007000               |

|                             |            |                                                              | 0x2400041C                                              |     | SPI               |                          |

|                             |            | DMA (7B)                                                     |                                                         |     |                   | 0x40006000               |

|                             |            |                                                              | 0x24000400                                              | l \ | UART              | 0x40005000               |

|                             | x00351FFF  | Unused                                                       |                                                         |     | Reserved          | 0x40004FFF               |

|                             |            |                                                              | 0x2400015F                                              |     |                   | 0x40003000               |

| FLASH B Alias (320kB        | 3) \       | MAC LUT (96B)                                                | 0X2400013F                                              | i i | Timer 2           | 0x40002000               |

| Program Memory              |            |                                                              | 0x24000100                                              | ) i | Timer 1           | 0x40001000               |

| (                           | 0x00302000 |                                                              | 0x240000FF                                              |     | Timer 0           | 0x4000000                |

|                             | x00301FFF  | MAC RAM (256B)                                               |                                                         |     |                   |                          |

| FLASH B Information         |            |                                                              |                                                         |     |                   |                          |

|                             | i i        |                                                              | 0x24000000                                              |     |                   |                          |

| Block Alias (8kB)           | 1          | Unused                                                       |                                                         |     |                   |                          |

| (                           | Dx00300000 |                                                              |                                                         | 1   |                   |                          |

| Unused                      |            |                                                              |                                                         |     |                   |                          |

|                             | x00251FFF  | FLASH Alias                                                  |                                                         |     |                   |                          |

| FLASH A Alias (320kB        |            |                                                              |                                                         |     |                   |                          |

|                             | ·/         |                                                              |                                                         |     |                   |                          |

| Program Memory              |            | Unused                                                       |                                                         |     |                   |                          |

|                             | Dx00202000 |                                                              | 0x00151FFF                                              |     |                   |                          |

|                             | x00201FFF  |                                                              |                                                         |     |                   |                          |

| FLASH A Information         |            | FLASH B (320kB)                                              | )                                                       |     | NCS36             | \$510                    |

| Block Alias(8kB)            |            | Program Memory                                               |                                                         |     |                   |                          |

| Bootloader and Factory Trim |            | · · · · · · · · · · · · · · · · · · ·                        | 0x00102000                                              |     | Memory            | / Man                    |

| (                           | Dx00200000 |                                                              | 0x00101FFF                                              |     |                   |                          |

|                             |            |                                                              | 0,00101111                                              |     | Defa              | ult                      |

|                             |            | FLASH B Information Blo                                      | ck (8kB)                                                |     | Dola              | ant                      |

|                             |            |                                                              | . ,                                                     |     |                   |                          |

|                             |            |                                                              |                                                         |     |                   |                          |

|                             |            |                                                              | 0x00100000                                              |     |                   |                          |

|                             |            | Unused                                                       | 0x00100000                                              |     |                   |                          |

|                             |            | Unused                                                       |                                                         |     |                   |                          |

|                             |            |                                                              | 0x00051FFF                                              |     |                   |                          |

|                             |            | Unused<br>FLASH A (320kB)                                    | 0x00051FFF                                              |     |                   |                          |

|                             |            |                                                              | 0x00051FFF                                              |     |                   |                          |

|                             |            | FLASH A (320kB)                                              | 0x00051FFF                                              |     |                   |                          |

|                             |            | FLASH A (320kB)                                              | 0x00051FFF<br>0x00002000                                |     |                   |                          |

|                             |            | FLASH A (320kB)<br>Program Memory                            | 0x00051FFF<br>0x00002000<br>0x00001FFF                  |     |                   |                          |

|                             |            | FLASH A (320kB)<br>Program Memory<br>FLASH A Information Blo | 0x00051FFF<br>0<br>0x00002000<br>0x00001FFF<br>ck (8kB) |     |                   |                          |

|                             |            | FLASH A (320kB)<br>Program Memory                            | 0x00051FFF<br>0<br>0x00002000<br>0x00001FFF<br>ck (8kB) |     |                   |                          |

|                             |            | FLASH A (320kB)<br>Program Memory<br>FLASH A Information Blo | 0x00051FFF<br>0<br>0x00002000<br>0x00001FFF<br>ck (8kB) |     |                   |                          |

Figure 2. Default Memory Map

Figure 3. Remapped Memory Map

| Peripheral Register      | Address     | Access | Description                                                                                      |

|--------------------------|-------------|--------|--------------------------------------------------------------------------------------------------|

| TIMER 0                  |             |        |                                                                                                  |

| Load                     | 0x4000_0000 | R/W    | Initial timer value                                                                              |

| Value                    | 0x4000_0004 | RO     | Current value of the timer                                                                       |

| Control                  | 0x4000_0008 | R/W    | Provides enable/disable, mode, and prescale configuration                                        |

| Clear                    | 0x4000_000C | WO     | Clears the interrupt                                                                             |

| TIMER 1                  |             |        | · · ·                                                                                            |

| Load                     | 0x4000_1000 | R/W    | Initial timer value                                                                              |

| Value                    | 0x4000_1004 | RO     | Current value of the timer                                                                       |

| Control                  | 0x4000_1008 | R/W    | Provides enable/disable, mode, and prescale configuration                                        |

| Clear                    | 0x4000_100C | WO     | Clears the interrupt                                                                             |

| TIMER 2                  | ·           |        |                                                                                                  |

| Load                     | 0x4000_2000 | R/W    | Initial timer value                                                                              |

| Value                    | 0x4000_2004 | RO     | Current value of the timer                                                                       |

| Control                  | 0x4000_2008 | R/W    | Provides enable/disable, mode, and prescale configuration                                        |

| Clear                    | 0x4000_200C | WO     | Clears the interrupt                                                                             |

| UART 1                   |             |        |                                                                                                  |

| Receive data             | 0x4000_5000 | RO     | Receive data                                                                                     |

| Transmit data            | 0x4000_5000 | WO     | Transmit data                                                                                    |

| Divisor latch LSB        | 0x4000_5000 | RW     | Least significant byte for input to baud generator                                               |

| Divisor latch MSB        | 0x4000_5004 | RW     | Most significant byte for input to baud generator                                                |

| Interrupt enable         | 0x4000_5004 | RO     | UART interrupt enables                                                                           |

| Interrupt identification | 0x4000_5008 | RO     | UART interrupt type/status register                                                              |

| FIFO control             | 0x4000_500C | WO     | Enable FIFOs, clear FIFOs, etc.                                                                  |

| Line control             | 0x4000_500C | RW     | Specifies asynchronous data communications exchange format and sets the divisor latch access bit |

| Modem control            | 0x4000_5010 | RW     | Controls interface with the modem                                                                |

| Line status              | 0x4000_5014 | RO     | Data transfer status information                                                                 |

| Modem status             | 0x4000_5018 | RO     | Current state of modem control lines                                                             |

| Scratch register         | 0x4000_501C | RW     | Modem scratch register                                                                           |

| SPI 1                    | ·           |        |                                                                                                  |

| Transmit data            | 0x4000_6000 | R/W    | Transmit data                                                                                    |

| Receive data             | 0x4000_6004 | R/W    | Receive data                                                                                     |

| Serial clock divisor     | 0x4000_6008 | R/W    | SPI block clock divider setting (divide MCU clock)                                               |

| Control                  | 0x4000_600C | R/W    | SPI control register                                                                             |

| Status                   | 0x4000_6010 | RO     | SPI status register                                                                              |

| Slave select             | 0x4000_6014 | R/W    | SPI slave select control                                                                         |

| Slave select polarity    | 0x4000_6018 | R/W    | SPI slave select polarity                                                                        |

| Interrupt enable         | 0x4000_601C | R/W    | SPI interrupt enables                                                                            |

| Interrupt status         | 0x4000_6020 | RO     | SPI interrupt status register                                                                    |

| Interrupt clear          | 0x4000_6024 | WO     | SPI interrupts clear register                                                                    |

| Peripheral Register      | Address         | Access | Description                                                                                      |

|--------------------------|-----------------|--------|--------------------------------------------------------------------------------------------------|

| SPI 1                    | - I             |        | · · · ·                                                                                          |

| Transmit FIFO watermark  | 0x4000_6028     | R/W    | Set watermark for transmit FIFO half full flag                                                   |

| Receive FIFO watermark   | 0x4000_602C     | R/W    | Set watermark for receive FIFO half full flag                                                    |

| Transmit FIFO level      | 0x4000_6030     | RO     | Transmit FIFO level                                                                              |

| Receive FIFO level       | 0x4000_6034     | RO     | Receive FIFO level                                                                               |

| I2C 1                    |                 |        |                                                                                                  |

| Status                   | 0x4000_7000     | RO     | I2C status register, clears upon read                                                            |

| Read data                | 0x4000_7004     | RO     | Read data FIFO access                                                                            |

| Command                  | 0x4000_7008     | WO     | I2C configuration                                                                                |

| Interrupt Enable         | 0x4000_700C     | R/W    | Enable or disable I2C interrupts                                                                 |

| Control                  | 0x4000_7010     | R/W    | I2C control                                                                                      |

| Prescale                 | 0x4000_7014     | R/W    | I2C block clock divider setting (divide MCU clock)                                               |

| UART 2                   |                 |        |                                                                                                  |

| Receive data             | 0x4000_8000     | RO     | Receive data                                                                                     |

| Transmit data            | 0x4000_8000     | WO     | Receive data                                                                                     |

| Divisor latch LSB        | 0x4000_8000     | RW     | Least significant byte for input to baud generator                                               |

| Divisor latch MSB        | 0x4000_8004     | RW     | Most significant byte for input to baud generator                                                |

| Interrupt enable         | 0x4000_8004     | RO     | UART interrupt enables                                                                           |

| Interrupt identification | 0x4000_8008     | RO     | UART interrupt type/status register                                                              |

| FIFO control             | 0x4000_800C     | WO     | Enable FIFOs, clear FIFOs, etc.                                                                  |

| Line control             | 0x4000_800C     | RW     | Specifies asynchronous data communications exchange format and sets the divisor latch access bit |

| Modem control            | 0x4000_8010     | RW     | Controls interface with the modem                                                                |

| Line status              | 0x4000_8014     | RO     | Data transfer status information                                                                 |

| Modem status             | 0x4000_8018     | RO     | Current state of modem control lines                                                             |

| Scratch register         | 0x4000_801C     | RW     | Modem scratch register                                                                           |

| SPI 2                    |                 |        | ·                                                                                                |

| Transmit data            | 0x4000_9000     | R/W    | Transmit data                                                                                    |

| Receive data             | 0x4000_9004     | R/W    | Receive data                                                                                     |

| Serial clock divisor     | 0x4000_9008     | R/W    | SPI block clock divider setting (divide MCU clock)                                               |

| Control                  | 0x4000_900C     | R/W    | SPI control register                                                                             |

| Status                   | 0x4000_9010     | RO     | SPI status register                                                                              |

| Slave select             | 0x4000_9014     | R/W    | SPI slave select control                                                                         |

| Slave select polarity    | 0x4000_9018     | R/W    | SPI slave select polarity                                                                        |

| Interrupt enable         | 0x4000_901C     | R/W    | SPI interrupt enables                                                                            |

| Interrupt status         | 0x4000_9020     | RO     | SPI interrupt status register                                                                    |

| Interrupt clear          | 0x4000_9024     | WO     | SPI interrupts clear register                                                                    |

| Transmit FIFO watermark  | 0x4000_9028     | R/W    | Set watermark for transmit FIFO half full flag                                                   |

| Receive FIFO watermark   | 0x4000_902C     | R/W    | Set watermark for receive FIFO half full flag                                                    |

| Transmit FIFO level      | 0x4000_9030     | RO     | Transmit FIFO level                                                                              |

| Receive FIFO level       | <br>0x4000_9034 | RO     | Receive FIFO level                                                                               |

| Peripheral Register                 | Address     | Access              | Description                                                                                                                              |

|-------------------------------------|-------------|---------------------|------------------------------------------------------------------------------------------------------------------------------------------|

| WDT                                 |             |                     |                                                                                                                                          |

| Load                                | 0x4000_A000 | R/W                 | Timer load value                                                                                                                         |

| Value                               | 0x4000_A004 | RO                  | Timer current value                                                                                                                      |

| Control                             | 0x4000_A008 | R/W                 | Enable                                                                                                                                   |

| Kick                                | 0x4000_A0C0 | WO                  | Kick (reload timer from load value)                                                                                                      |

| Lock                                | 0x4000_A100 | WO                  | Lock                                                                                                                                     |

| Status                              | 0x4000_A140 | [3] R/W<br>[2:0] RO | Status. Bit 3 is a R/W error bit (busy bit).                                                                                             |

| PWM                                 |             |                     |                                                                                                                                          |

| Duty Cycle                          | 0x4000_B000 | WO                  | Duty cycle configuration                                                                                                                 |

| Enable                              | 0x4000_B004 | WO                  | PWM output enable                                                                                                                        |

| Disable                             | 0x4000_B008 | WO                  | PWM output disable                                                                                                                       |

| Prescale enable                     | 0x4000_B00C | WO                  | Prescale select enable                                                                                                                   |

| Prescale disable                    | 0x4000_B010 | WO                  | Prescale select disable                                                                                                                  |

| Configuration and status            | 0x4000_B014 | RO                  | Read PWM configuration and status                                                                                                        |

| DIO                                 |             |                     |                                                                                                                                          |

| State/Set                           | 0x4000_C000 | R/W                 | Read to see current state of synchronized input<br>signals. Write ones to set corresponding outputs<br>to 1, writes of 0 have no effect. |

| Interrupts/Clear                    | 0x4000_C004 | R/W                 | Read to see current state of interrupts. Write<br>ones to set corresponding outputs to 0, writes of<br>0 have no effect.                 |

| Output Enable Set                   | 0x4000_C008 | WO                  | Write ones to set direction to output, writes of 0 have no effect on signal configuration                                                |

| Output Enable Clear –<br>Make input | 0x4000_C00C | WO                  | Write ones to set direction to input (clears output<br>enable), writes of 0 have no effect on signal con-<br>figuration                  |

| Enable interrupts set               | 0x4000_C010 | WO                  | Write ones to set enable interrupts, writes of 0 have no effect on interrupts configuration                                              |

| Enable interrupts clear             | 0x4000_C014 | WO                  | Write ones to set disable interrupts, writes of 0 have no effect on interrupts configuration                                             |

| Edge interrupts select              | 0x4000_C018 | WO                  | Write ones to set interrupt to edge-sensitive,<br>writes of 0 have no effect on interrupts configura-<br>tion                            |

| Level interrupts select             | 0x4000_C01C | WO                  | Write ones to set interrupt to level-sensitive,<br>writes of 0 have no effect on interrupts configura-<br>tion                           |

| Level interrupts set                | 0x4000_C020 | WO                  | Write ones to set interrupts to active high or rising edge, writes of 0 have no effect on interrupts con-<br>figuration                  |

| Level interrupts clear              | 0x4000_C024 | WO                  | Write ones to clear interrupt for active low or fall-<br>ing edge, writes of 0 have no effect on interrupts<br>configuration             |

| Any edge interrupts set             | 0x4000_C028 | WO                  | Write ones to override interrupt edge selection<br>and interrupt on any edge, writes of 0 have no<br>effect on interrupts configuration  |

| Any edge interrupts clear           | 0x4000_C02C | WO                  | Write ones to clear edge selection override, writes<br>of 0 have no effect on interrupts configuration                                   |

| Interrupts clear                    | 0x4000_C030 | WO                  | Write ones to clear edge sensitive interrupts,<br>writes of 0 have no effect on interrupts configura-<br>tion                            |

| Peripheral Register | Address     | Access | Description                                                                                       |

|---------------------|-------------|--------|---------------------------------------------------------------------------------------------------|

| DIO                 |             |        |                                                                                                   |

| Control             | 0x4000_C034 | WO     | Controls loopback/normal mode operation                                                           |

| I2C 2               |             |        | ·                                                                                                 |

| Status              | 0x4000_D000 | RO     | I2C status register, clears upon read                                                             |

| Read data           | 0x4000_D004 | RO     | Read data FIFO access                                                                             |

| Command             | 0x4000_D008 | WO     | I2C configuration                                                                                 |

| Interrupt enable    | 0x4000_D00C | R/W    | Enable or disable I2C interrupts                                                                  |

| Control             | 0x4000_D010 | R/W    | I2C control                                                                                       |

| Prescale            | 0x4000_D014 | R/W    | I2C block clock divider setting (divide MCU clock)                                                |

| RTC                 |             |        | ·                                                                                                 |

| Sub-second counter  | 0x4000_F000 | R/W    | Sub-second counter. A write loads the written value and a read returns the current counter value. |

| Second counter      | 0x4000_F004 | R/W    | Second counter. A write loads the written value and a read returns the current counter value.     |

| Sub-second alarm    | 0x4000_F008 | R/W    | Sub-second alarm value                                                                            |

| Second alarm        | 0x4000_F00C | R/W    | Second alarm value                                                                                |

| RTC control         | 0x4000_F010 | R/W    | Control register for enables and interrupts                                                       |

| RTC status          | 0x4000_F014 | WO/RO  | Status register for errors, busy, and interrupts                                                  |

| RTC clear           | 0x4000_F018 | WO     | Clears the interrupt status                                                                       |

| CROSSBAR (XBAR)     |             |        |                                                                                                   |

| DIO[0] control      | 0x4001_0000 | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[1] control      | 0x4001_0004 | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[2] control      | 0x4001_0008 | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[3] control      | 0x4001_000C | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[4] control      | 0x4001_0010 | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[5] control      | 0x4001_0014 | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[6] control      | 0x4001_0018 | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[7] control      | 0x4001_001C | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[8] control      | 0x4001_0020 | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[9] control      | 0x4001_0024 | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[10] control     | 0x4001_0028 | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[11] control     | 0x4001_002C | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[12] control     | 0x4001_0030 | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[13] control     | 0x4001_0034 | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[14] control     | 0x4001_0038 | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[15] control     | 0x4001_003C | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[16] control     | 0x4001_0040 | R/W    | Crossbar settings for given DIO pin                                                               |

| DIO[17] control     | 0x4001_0044 | R/W    | Crossbar settings for given DIO pin                                                               |

| TRNG                | ı L         |        |                                                                                                   |

| Value               | 0x4001_1000 | R/W    | On a write sets the seed value, on a read returns random number                                   |

| Control             | 0x4001_1004 | R/W    | Control register                                                                                  |

| Peripheral Register          | Address             | Access           | Description                                                         |

|------------------------------|---------------------|------------------|---------------------------------------------------------------------|

| TRNG                         | I                   |                  |                                                                     |

| Write buffer LSW             | 0x4001_1008         | R/W              | Byte swap write buffer - Least significant word                     |

| Write buffer MSW             | 0x4001_100C         | R/W              | Byte swap write buffer – Most significant word                      |

| Read buffer LSW              | 0x4001_1010         | RO               | Byte swap read buffer – Least significant word                      |

| Read buffer MSW              | 0x4001_1014         | RO               | Byte swap read buffer – Most significant word                       |

| Meta-stable latch TRNG value | 0x4001_1018         | RO               | Meta-stable latch TRNG value                                        |

| White noise TRNG value       | 0x4001_101C         | RO               | White noise TRNG value                                              |

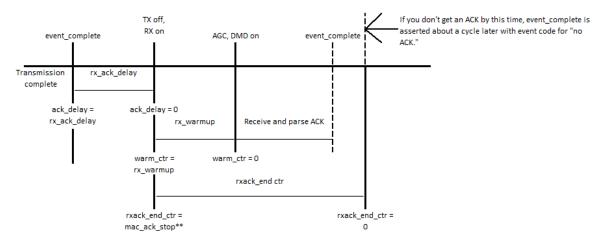

| IEEE 802.15.4 MEDIUM ACC     | ESS CONTROL (MAC) - | EXPERT REGISTERS |                                                                     |

| Sequencer                    | 0x4001_4000         | R/W              | Used to control MAC sequence operation                              |

| Sequence options             | 0x4001_4004         | R/W              | Set options that change behavior of basic events                    |

| Control                      | 0x4001_4008         | R/W              | Control register                                                    |

| Status                       | 0x4001_4010         | RO               | Status register                                                     |